# **Applied Informatics**

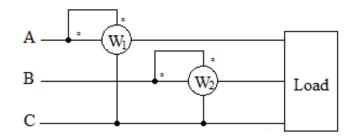

Editors: Leonids Ribickis, Nadezhda Kunicina

Peteris Apse-Apsitis Nadezhda Kunicina

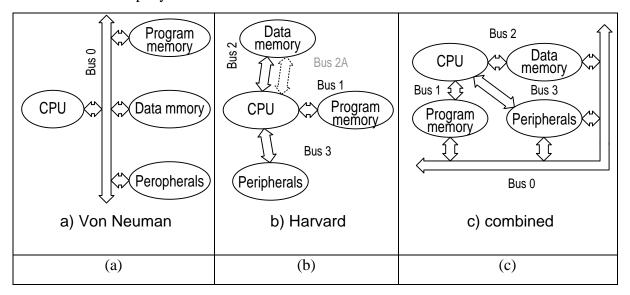

Boris Assanovic Viktar Liauchuk

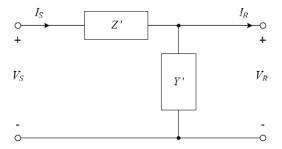

Jelena Caiko Leonids Ribickis

Ilja Galkins Andrei Varuyeu

Dmitry Kovalenko Anatolijs Zabasta

Elias Kyriakides Anastasija Zhiravecka

This document has been prepared by the financial support of European Union. The authors from Riga Technical University and Belarusian State University are responsible for the content of this document. This publication reflects the views only of the authors, and it cannot be regarded as the European Union's official position.

The book is developed in a frame of the project "ERASMUS+ Capacity-building in the Field of Higher Education 2015 Call for Proposals EAC/A04/2014 561525-EPP-1-2015-1-LV-EPPKA2-CBHE-JP - ERASMUS+ CBHE.

The textbook is devised for students of applied physic and electrical engineering specialties. The textbook can be useful for students and professionals focusing on applied informatics issues. The book gives overview of current computer control of electrical technologies and IT elements, as well as explains their operating principles.

**Key Action:** KA2 - Cooperation for innovation and the exchange of good practices

**Action:** Capacity Building in Higher Education

**Action Type:** Joint Projects

**Deliverable:** 2.3. Five electronic courses e-Books by the declared directions

Project Scientific Manager: Nadezhda Kunicina

Project Coordinator: Anatolijs Zabasta

Editors: Leonids Ribickis, Nadezhda Kunicina

**Institution:** Riga Technical University

Under the Creative Commons Attribution license, the authors and users are free to share (copy and redistribute the material in any medium of format) and adapt (remix, transform and build upon the material for any purpose, even commercially) this work. The licensor cannot revoke these freedoms as long as you follow the license terms.

ISBN - 978-9934-22-144-6 (pdf)

# **Contributors**

**Peteris Apse-Apsitis**, associate professor, senior researcher. Head of Division of Industrial Electronic equipment of Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Faculty of Power and Electrical Engineering, 12/1 Azenes Str. - 510., Riga, LV 1048, Latvia, tel. +371 67089917, peteris.apse-apsitis@rtu.lv

**Boris Assanovich**, associate professor in the Department of Information Systems and Technologies, at YK State University of Grodno, Physics and Technical Faculty Coordinator of International Academic and Project Activity office: YKSUG Laboratory Campus, BLK-5, 107, Grodno 230009, Belarus, tel. +375 152431279, bas@grsu.by

**Jelena Caiko**, senior researcher of Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Faculty of Power and Electrical Engineering, 12/1 Azenes Str. - 503., Riga, LV 1048, Latvia, jelena.caiko@rtu.lv

**Ilja Galkins,** professor, senior researcher of Division of Industrial Electronic equipment, Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Faculty of Power and Electrical Engineering, 12/1 Azenes Str. - 502., Riga, LV 1048, Latvia, tel. +371 67089918, ilja.galkins@rtu.lv

**Dmitry Kovalenko**, dean of the Faculty of Physics and Information Technology, Francisk Skorina Gomel State University, 102 Sovetskaya Str., off. 2-9, Gomel, Belarus, 246019, tel. +375 232576557, dkov@gsu.by

**Elias Kyriakides,** associate professor in the Department of Electrical and Computer Engineering and the Associate Director for Research of the KIOS Research Center for Intelligent Systems and Networks, at the University of Cyprus. Office 1: Green Park 408, KIOS Research Center, Nicosia, Cyprus tel. +357 22892291, elias@ucy.ac.cy

**Nadezhda Kunicina**, professor, senior researcher of Division of Industrial Electronic equipment, Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Faculty of Power and Electrical Engineering, 12/1 Azenes Str. - 503., Riga, LV 1048, Latvia, tel. +371 67089052, nadezda.kunicina@rtu.lv

**Viktar Liauchuk**, associate professor. Head of the Department of Automated systems of information processing, Francisk Skorina Gomel State University, 102 Sovetskaya Str., off. 4-7, Gomel, Belarus, 246019, liauchuk@gmail.com

**Leonids Ribickis,** professor, rector of Riga Technical University, Head of Institute of Industrial Electronics and Electrical engineering, Faculty of Power and Electrical Engineering, Riga Technical University, Scientific Head of Electromechatronics Scientific laboratory, 1, Kalku Str. -217, Riga, LV 1658, Latvia, tel. +371 67089300, leonids.ribickis@rtu.lv

**Andrei Varuyeu,** associate professor of the Department of Automated systems of information processing, Francisk Skorina Gomel State University, 102 Sovetskaya Str., off. 4-7, Gomel, Belarus, 246019, +375 232578863, ang@gsu.by

**Anatolijs Zabasta**, senior researcher of Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Faculty of Power and Electrical Engineering, 12/1 Azenes Str. - 503., Riga, LV 1048, Latvia, tel. +371 67089051, anatolijs.zabashta@rtu.lv

**Anastasija Zhiravecka,** professor, senior researcher of Division of Industrial Electronic equipment, Institute of Industrial Electronics and Electrical Engineering, Riga Technical University, Faculty of Power and Electrical Engineering, 12/1 Azenes Str. - 509., Riga, LV 1048, Latvia, tel. +371 67089917, anastasija.zhiravecka@rtu.lv

# Content

| Introduction | 1                                                                                                     | 8   |

|--------------|-------------------------------------------------------------------------------------------------------|-----|

| Chapter 1:   | Information and Communication Technologies                                                            | 10  |

| 1.1. Con     | mmunication network design and operational characteristics                                            | 11  |

| 1.1.1.       | Introduction                                                                                          | 11  |

| 1.1.2.       | Telecommunications basics                                                                             | 11  |

| 1.1.3.       | Wireless sensor networks in smart metering                                                            | 41  |

| 1.1.4.       | WSN standards and technologies                                                                        | 45  |

| 1.1.5.       | Application domains and deployments                                                                   | 51  |

| 1.1.6.       | Factors influencing sensor network design                                                             | 55  |

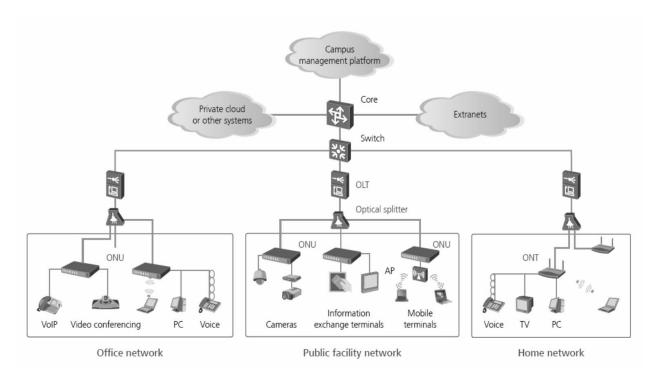

| 1.1.7.       | A passive optical network (PON)                                                                       | 59  |

| 1.2. Co      | mputer Networks a systems approach                                                                    | 61  |

| 1.2.1.       | Data to signal conversion in computer network                                                         | 61  |

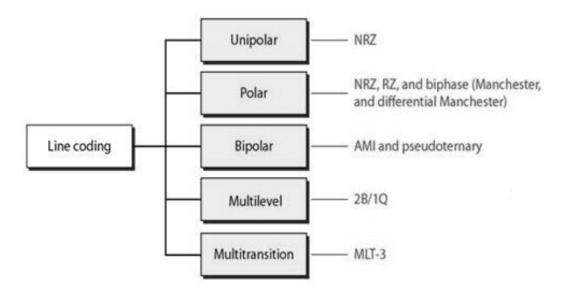

| 1.2.2.       | Line Coding Schemes                                                                                   | 62  |

| 1.2.3.       | Data Link Control                                                                                     | 68  |

| 1.2.4.       | Error and Flow Control                                                                                | 70  |

| 1.2.5.       | Random Access                                                                                         | 79  |

| 1.2.6.       | Multiuser Access in Networks                                                                          | 81  |

|              | mputer networks architecture and design, using standard and specific ad<br>inication network elements | -   |

| 1.3.1.       | Network Components                                                                                    | 92  |

| 1.3.2.       | The OSI Model                                                                                         | 94  |

| 1.3.3.       | Protocol Notations                                                                                    | 100 |

| 1.3.4.       | Local Area Networks                                                                                   | 103 |

| 1.4. Spe     | ecialized telecommunications networks, the use for infrastructure control                             | 107 |

| 1.4.1.       | State-of-the-art meter reading                                                                        | 107 |

| 1.4.3.       | Wire-line technologies                                                                                | 108 |

| 1.4.4.       | Powerline communications (PLC)                                                                        | 111 |

| 1.4.5.       | Wireless technologies                                                                                 | 113 |

| 1.4.6.       | Open data/application models' standards                                                               | 120 |

| 1.5.   | Solution of problems caused by Layer 1 Redundancy of communication   |           |

|--------|----------------------------------------------------------------------|-----------|

| 1.5    | .1. Reliability of systems with redundancy of communication channels | 122       |

| 1.5    | .2. Increase in the number of copies of transmitted data             | 123       |

| 1.5    | .3. Spanning Tree Algorithm                                          | 125       |

| 1.5    | .4. Aggregation of communication channels                            | 130       |

| 1.5    | .5. Aggregation of communication devices                             | 131       |

| Chapte | r 2: Control Theory                                                  | 133       |

| 2.1.   | Basics of Control Theory                                             | 134       |

| 2.2.   | Concept of Transfer Function                                         | 136       |

| 2.3.   | Types of Controllers and Their Description                           | 139       |

| 2.4.   | Evaluation of Regulated System Stability                             | 147       |

| 2.4    | .1. Rauss-Gurvits stability criterion                                | 148       |

| 2.4    | .2. Nyquist criterion of stability                                   | 148       |

| 2.5.   | Qualitative Parameters of System Stability                           | 150       |

| Chapte | r 3: Microcontrollers                                                | 153       |

| 3.1.   | Embedded systems with microcontrollers                               | 154       |

| 3.2.   | Architectures of MCUs, their main parameters, most popular MCUs pre  | sented on |

| marke  | et                                                                   | 156       |

| 3.3.   | Rules of successful MCU handling                                     | 160       |

| 3.4.   | Operation of CPU                                                     |           |

| 3.5.   | Peripheral devices of MCUs                                           | 192       |

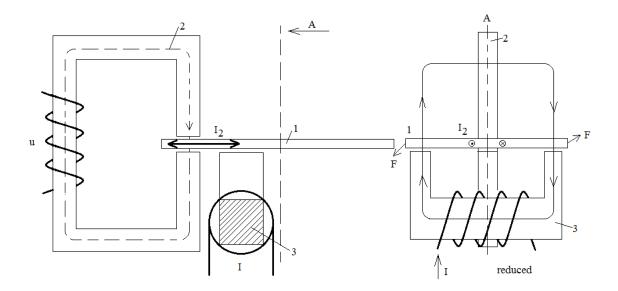

| Chapte | r 4: Electrical engineering and automation                           | 202       |

| 4.1.   | Principles and applications                                          | 203       |

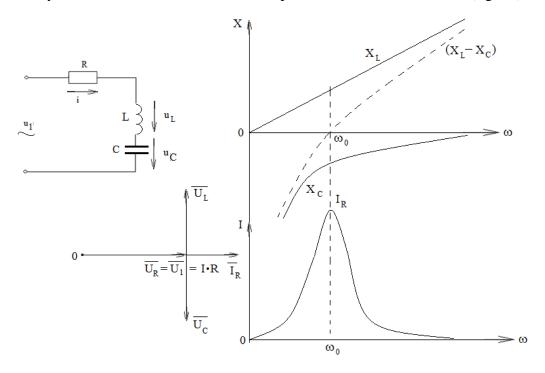

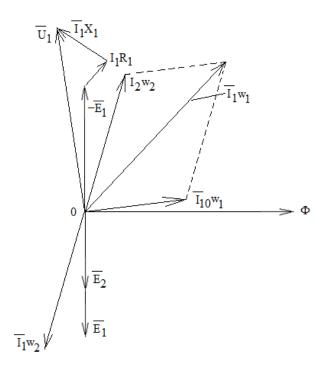

| 4.1    | .1. Resonance phenomenon in AC electrical circuits                   | 203       |

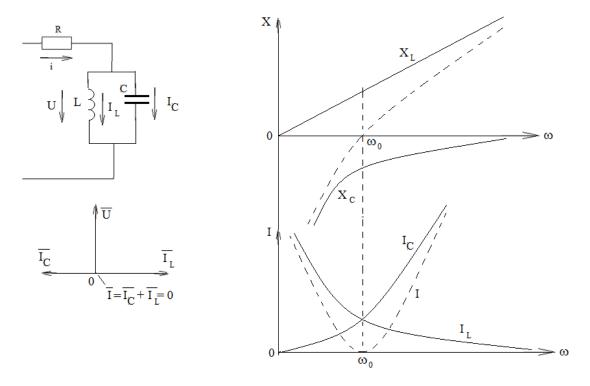

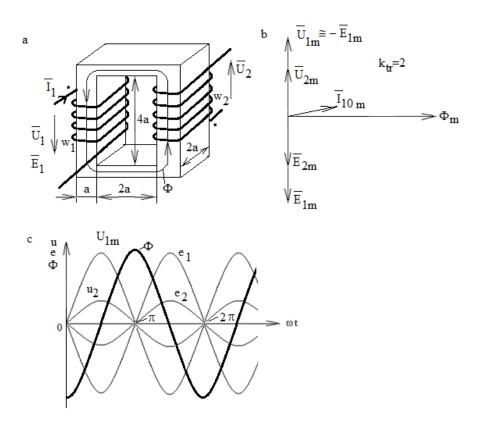

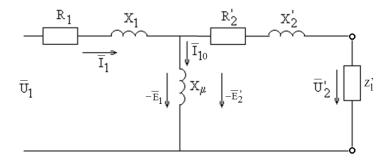

| 4.1    | .2. Single-Phase Transformer                                         | 205       |

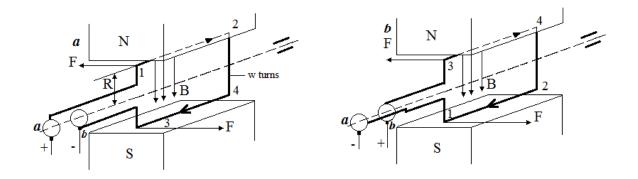

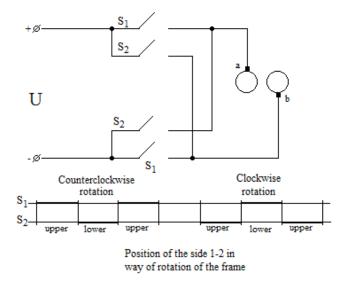

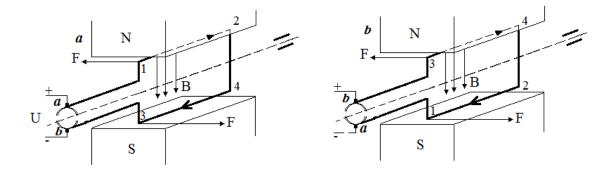

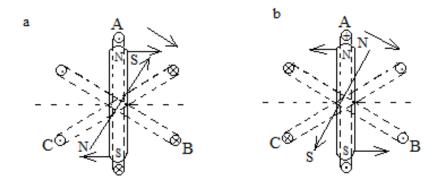

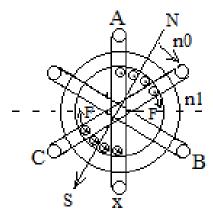

| 4.1    | .3. Basic realisation of electrical motor                            | 208       |

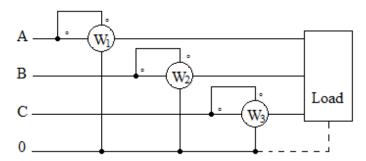

| 4.1    | .4. Measurements of active power and energy in AC circuits           | 214       |

| 4.1    | .5. Measurement of power in three-phase electrical circuits          | 215       |

| 4.1    | .6. Three-phase electrical motor                                     | 217       |

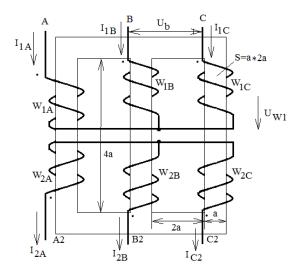

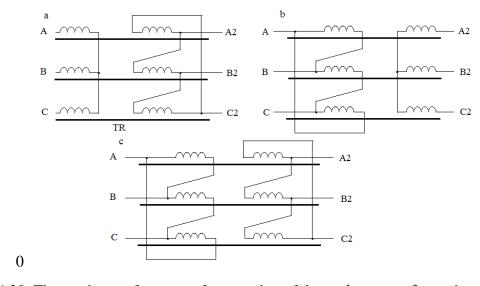

| 4.1    | .7. Three-phase transformer                                          | 220       |

| 42     | Means of automation in electrical systems                            | 224       |

| References                                          | 256 |

|-----------------------------------------------------|-----|

| 4.2.4. Microprocessor means of automation           | 249 |

| 4.2.3. Sensors                                      | 241 |

| 4.2.2. Converters of voltage, current and frequency | 235 |

| 4.2.1. Parameters and characteristics of elements   | 224 |

# Introduction

The book "Applied Informatics" provides a technical background for students of applied physic and electrical engineering specialties. The book is addressed for all level of students and developers of electromechanical devices, automotive control schemes, motion control solutions, as well as a high level of automated infrastructure management technologies. The book is helpful to the development of modern intelligent systems and sensors network, using high-performance computing technology for signal processing, as well for the development of data collection devices, for development of models, methods and metrics that enable quantitative evaluation of electric power and telecommunications infrastructure critical impact and interdependences.

Modern industrial production and manufacturing systems have evolved in basically four generations. The first generation that enabled the industrial revolution dates back to around 1850 or so. The use of steam-powered machines enabled mass production of gods such as clothes, cars and many other products in the beginning of the 20th century (Delsing J., 2017). In the second generation, the use of efficient pneumatic systems became a widely adopted solution for mass-production. The combined use of pneumatic valves and sensors enabled automatic production systems to be used in industrial applications. The third generation systems evolved from pneumatic to electrical motors. The use of electricity as the energy source enabled even newer types of automatic control systems to be developed. Sensors and actuators were now connected to new types of monitoring and control systems like Distributed Control Systems, DCS and Supervisory Control and Data Acquisition, SCADA using technologies such as field buses. The hierarchical approach of device-level, DCS, and SCADA (known as ISA-95), soon became the de-facto architectural style for how industrial productions systems were designed and deployed. DCS and SCADA systems soon became networked, which enabled tight integration between control systems and Enterprise Resource Planning Systems (ERP) and Manufacturing execution system (MES). This is today the most widely used approach by the industry and has been so for at least the last 20-30 years. In the 90'ths the current state of the art architecture ISA-95 was established. Seemingly, the size of ISA-95 based automation systems was limited in respect of I/O points. This becomes a technology bottleneck in the view of the upcoming smart cities and smart energy grids.

The book is useful for students, who study industrial production lines and control tools developed in all generations. The book is also exploring the problems associated with modelling of an ongoing urban environment process in order to ensure a high level of automated infrastructure management, intelligent systems and sensors network technology.

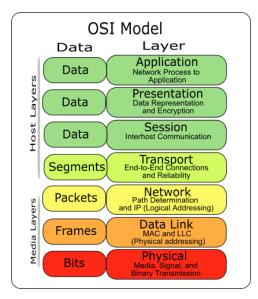

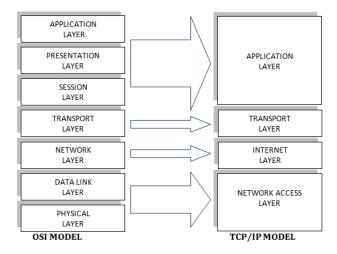

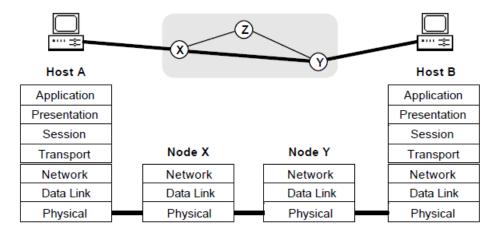

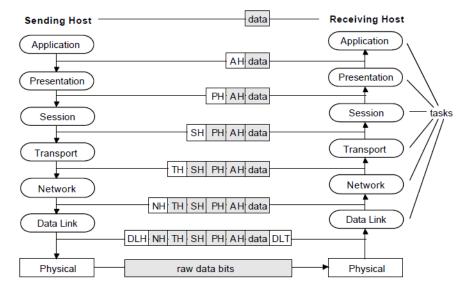

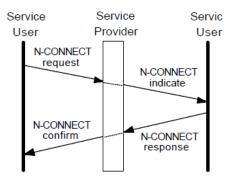

The Chapter 1 of this book is devoted to communication networks with the clear focus on computer networks architecture, design, network standards and specific network elements. The goal of this chapter is to present the basics concepts of telecommunication systems, including OSI, network components, quality issues of network design, model with focus on digital and wireless, and the most important features of the propagation of telecommunication signals, as well as computer networks architecture and design, using standard and specific adaptive telecommunication network elements, and its application domains and deployments.

The Chapter 2 of this book is devoted to control theory, including evaluation of regulated system stability, qualitative parameters of system stability. The chapter addresses an issues of the automation control, in particular process of a technical object control without a human involvement. Additionally, the object should be able to perceive the control signals containing the information about the further object condition. In most of the cases these signals are generated on the basis of the information about the current condition of the object. Therefore, the flows of information and their relations are the basis of the automatic control process.

The Chapter 3 of this book is devoted to microcontrollers, in particular it explains, how design embedded systems with microcontrollers, the architectures of MCUs, main parameters, most popular MCUs presented on market, and peripheral devices of MCUs. The chapter describes specific of control systems, which contain actuators, sensors and microcontrollers, included in the devices. Case studies describe design and application of such embedded control systems.

The Chapter 4 of this book is devoted to general aspects of electrical engineering and automation, starting with principles, applications, and detailed explanation of main features of the physical background and elements of automation, like resonance phenomenon in AC electrical circuits, main principles of single-phase transformer, and basic realisation of electrical motor. The chapter describes measurements of active power and energy in AC circuits, measurements of power in three-phase electrical circuits, three-phase electrical motors, the means of automation in electrical systems as well as sensors and microprocessor applied in automation.

# Chapter 1: Information and Communication Technologies

# 1.1. Communication network design and operational characteristics

#### 1.1.1. Introduction

The Chapter 1 of this book is devoted to communication networks with the clear focus on computer networks architecture, design, network standards and specific network elements.

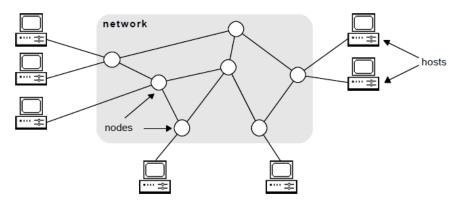

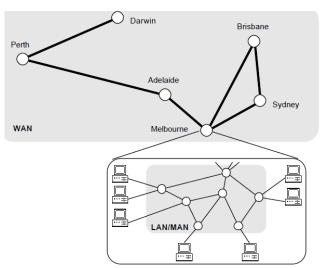

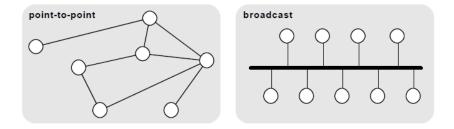

Before we can understand how to design a computer network, we should first agree on exactly what a computer network is. At one time, the term network meant the set of serial lines used to attach dumb terminals to mainframe computers. Other important networks include the voice telephone network and the cable TV network used to disseminate video signals. The main things these networks have in common are that they are specialized to handle one particular kind of data.

What distinguishes a computer network from these other types of networks? Probably the most important characteristic of a computer network is its generality. Computer networks are built primarily from general-purpose programmable hardware, and they are not optimized for a particular application like making phone calls or delivering television signals. Instead, they are able to carry many different types of data, and they support a wide, and ever growing, range of applications. Today's computer networks are increasingly taking over the functions previously performed by single-use networks. This chapter looks at some typical applications of computer networks and discusses the requirements that a network designer who wishes to support such applications must be aware of (Computer Networks 2012).

# 1.1.2. Telecommunications basics

The goal of this chapter is to present the basics concepts of telecommunication systems with focus on digital and wireless, and the most important features of the propagation of telecommunication signals.

#### Basic concepts include:

- Signal: Analog, Digital, Random

- Sampling

- Bandwidth

- Spectrum

- Noise

- Interference

- Channel Capacity

- BER

- Modulation

The purpose of any telecommunications system is to transfer information from the sender to the receiver by a means of a communication channel.

Let us talk a bit about what a signal actually is electronic signals specifically (as opposed to traffic signals, albums by the ultimate power-trio, or a general means for communication). The signals we are talking about are time-varying "quantities" which convey some sort of information. In electrical engineering the quantity that's time-varying is usually voltage (if not that, then usually current). So, when we talk about signals, just think of them as a voltage that is changing over time.

Signals are passed between devices in order to send and receive information, which might be video, audio, or some sort of encoded data. Usually the signals are transmitted through wires, but they could also pass through the air via radio frequency (RF) waves. Audio signals, for example might be transferred between your computer's audio card and speakers, while data signals might be passed through the air between a tablet and a Wi-Fi router (PSCES, 2012).

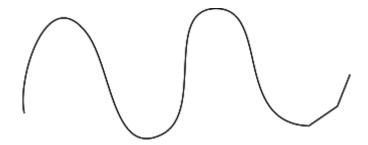

## **Analog signal**

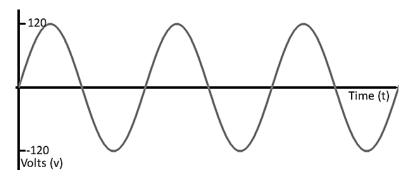

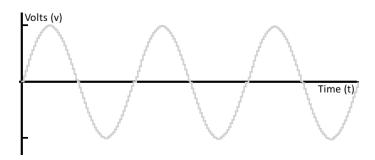

Because a signal varies over time, it is helpful to plot it on a graph where time is plotted on the horizontal, x-axis, and voltage on the vertical, y-axis. Looking at a graph of a signal is usually the easiest way to identify if it is analog or digital; a time-versus-voltage graph of an analog signal should be smooth and continuous.

Figure 1.1. An analogue signal graph

While these signals may be limited to a range of maximum and minimum values, there are still an infinite number of possible values within that range.

For example, the analogue voltage coming out of your wall socket might be clamped between -120V and +120V, but, as you increase the resolution more and more, you discover an infinite number of values that the signal can actually be (like 64.4V, 64.42V, 64.424V, and infinite, increasingly precise values).

For analogue signals, these variations are directly proportional to some physical variable like sound, light, temperature, wind speed, etc.

Pure audio signals are also analogue. The signal that comes out of a microphone is full of analogue frequencies and harmonics, which combine to make beautiful music.

#### **Example Analog Signals**

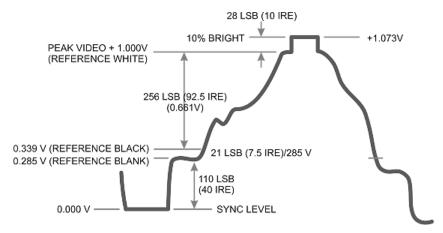

Video and audio transmissions are often transferred or recorded using analog signals. The composite video coming out of an old RCA jack, for example, is a coded analog signal usually ranging between 0 and 1.073V. Tiny changes in the signal have a huge effect on the color or location of the video.

Figure 1.2. An analogue signal representing one line of composite video data

#### **Characteristics of Analog Signal**

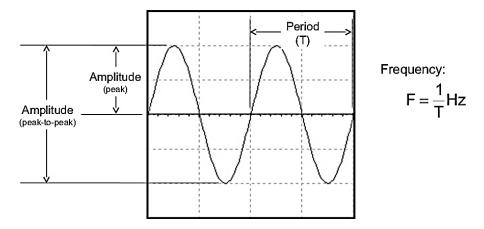

Figure 1.3. Characteristics of analogue signal

Information which is analog in its native form (audio and image) can vary continuously in terms of intensity (volume or brightness) and frequency (tone or color). Those variations in the native information stream are translated in an analog electrical network into variations in the amplitude and frequency of the carrier signal. In other words, the carrier signal is modulated (varied) in order to create an analog of the original information stream.

The electromagnetic sinusoidal (waveform) or sine wave can be varied in amplitude at a fixed frequency, using Amplitude Modulation (AM). Alternatively, the frequency of the sine wave can be varied at constant amplitude using Frequency Modulation (FM). Additionally, both frequency and amplitude can be modulated simultaneously.

- Analog signal can have infinite number of values and varies continuously with time.

- Analog signal is usually represented by sine wave.

- As shown in figure each cycle consists of a single arc above the time axis followed by a single arc below the time axis.

- Example of analogue signal is human voice. When we speak, we use air to transmit an analogue signal. Electrical signal from an audio tape, can also be in analogue form.

### **Amplitude**

- Amplitude of a signal refers to the height of the signal.

- It is equal to the vertical distance from a given point on the waveform to the horizontal axis.

- The maximum amplitude of a sine wave is equal to the highest value it reaches on the vertical axis as shown in figure.

- Amplitude is measured in volts, amperes or watts depending on the type of signal. A volt is used for voltage, ampere for current and watts for power.

#### Period

- Period refers to the amount of time in which a signal completes one cycle.

- It is measured in seconds.

- Other units used to measure period are millisecond (10-3 sec.) microsecond (10-6 sec), nanosecond (10-9 sec) and picoseconds (10-12 sec).

#### **Frequency**

- It refers to the number of wave patterns completed in a given period of time.

- To be more precise, frequency refers to number of periods in one second or number of cycles per second.

- Frequency is measured in Hertz (Hz)

- Other units used to express frequency are kilohertz (103 Hz) Megahertz (106 Hz), gigahertz (109 Hz) and terahertz (1012 Hz).

- Frequency and period are the inverse of each other. Period is the inverse of frequency and frequency is the inverse of period.

<u>Example</u>: The power we use at home has a frequency of 60 Hz. The period of this sine wave can be determined as follows:

Solution:

$$T = \frac{1}{f} = \frac{1}{60} = 0.0166s = 0.0166 \times 10^3 ms = 16.6 ms$$

Example: The period of a signal is 100 ms. What is its frequency in kilohertz?

Solution: First we change 100 ms to seconds, and then we calculate the frequency from the period (1 Hz =  $10^{-3}$  kHz).

$$100 ms = 100 \times 10^{-3} s = 10^{-1} s$$

$$f = \frac{1}{T} = \frac{1}{10^{-1}}Hz = 10Hz = 10 \times 10^{-3}kHz = 10^{-2}kHz$$

Example: A sine wave is offset 1/6 cycle with respect to time 0. What is its phase in degrees and radians?

Solution: We know that 1 complete cycle is 360°. Therefore, 1/6 cycle is

$$\frac{1}{6} \times 360 = 60^{\circ} = 60 \times \frac{2\pi}{360} rad = \frac{\pi}{3} rad = 1.046 rad$$

#### **Phase**

- Phase describes the position of the waveform relative to time zero.

- Phase describes the amount by which the waveform shifts forward or backward along the time axis.

- It indicates the status of first cycle.

- Phase is measured in degrees or radians.

A phase shift of 3600 indicates a shift of a complete period, a phase shift of 180° indicates a shift of half period and a phase shift of 90° indicates a shift of a quarter of a period as shown in fig. below.

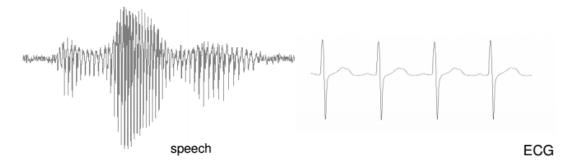

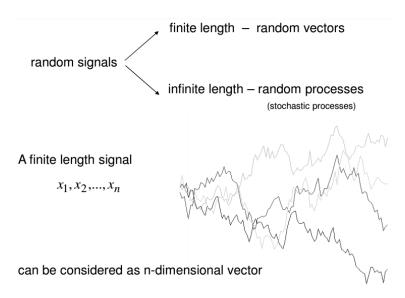

### Random signal

Random signal are the ones that are unpredictable and can be described only by statistical means. Many signals processed by computers can be considered as random.

Examples of random signal: speech, audio, video, digital communication, medical, biological, and economic signals.

Figure 1.4 Examples of random signals

# **Sampling**

The information can also be transmitted by digital binary signals that will have only two values, a digital one and a digital zero.

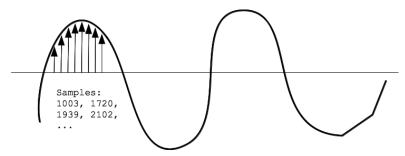

Any analogue signal can be converted into a digital signal by appropriately sampling and then coding it.

Figure 1.5. Sampling

The way an analog signal is brought into the computer is "digitization". The computer "samples" the signal very rapidly over time, noting the value (the height basically) of the curve each time, and recording that value as a number. CD quality audio samples the sound signal 44000 times per second, noting the "height" of the sound signal once for sample. Each sample is a whole number in the range -32768 .. 32767 (this is the range of number that can be stored in 2 bytes, 256 squared).

Audio CD digitization is very good, but not perfect. The signal might have a little wiggle that happens so fast, the 44000 samples/second are not fast enough to quite capture the wiggle perfectly. In reality, 44000 samples per second captures almost everything the human ear can hear anyway. There can also be a sort of rounding error -- the signal value might be in between 1452 and 1453, and the digitization has to pick just one value to represent it. As a practical matter, the 44000 samples per second is extremely good at capturing the level of detail that humans can hear.

So in essence, digitization translates a sound signal into just a series of numbers: 12000, 12002, 12006, 12007, 12010, 12005, 12006, ... and so on. Playing back the digital sound is just the reverse: a chip takes in the stream of numbers, say representing 44000 samples/second, and constructs an electrical signal that matches those numbers over time. In effect, this reconstructs the original sound signal from the numbers.

# Example:

Sound needs to be converted into binary for computers to be able to process it. To do this, sound is captured - usually by a microphone - and then converted into a digital signal.

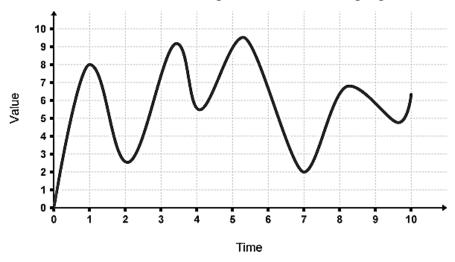

An analogue to digital converter will sample a sound wave at regular time intervals. For example, a sound wave like this can be sampled at each time sample point:

Figure 1.6. Sound representation

The samples can then be converted to binary. They will be recorded to the nearest whole number.

| Time<br>sample | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   |

|----------------|------|------|------|------|------|------|------|------|------|------|

| Denary         | 8    | 3    | 7    | 6    | 9    | 7    | 2    | 6    | 6    | 6    |

| Binary         | 1000 | 0011 | 0111 | 0110 | 1001 | 0111 | 0010 | 0100 | 0110 | 0110 |

If the time samples are then plotted back onto the same graph, it can be seen that the sound wave now looks different. This is because sampling does not take into account what the sound wave is doing in between each time sample.

Figure 1.7. Sampled signal of sound

This means that the sound loses quality, as data has been lost between the time samples. The way to increase the quality and store the sound at a quality closer to the original is to have more time samples that are closer together. This way, more detail about the sound can be collected, so when it is converted to digital and back to analogue again it does not lose as much quality.

The frequency at which samples are taken is called the sample rate, and is measured in Hertz (Hz). 1 Hz is one sample per second. Most CD-quality audio is sampled at 44 100 or 48 000 KHz.

The sampling frequency must be at least twice the maximum frequency present in the signal in order to carry all the information contained therein.

The minimum sampling rate required in order to accurately reconstruct the analogue input is given by the Nyquist sampling rate,  $f_N$ , given by the formula:

$$f_N = 2f_{max},\tag{1.1}$$

where  $f_{max}$  is the highest frequency component of the analogue input.

The Nyquist sampling rate (frequency) is the minimum. In practice, sampling rates are much higher, typically 2 times the Nyquist rate  $f_N$ . In other words, 4 times  $f_{max}$ .

Therefore, we say that the <u>sampling frequency</u> must be *more than* twice the value of the highest frequency component of the signal:

$$f_s \ge f_N$$

, where  $f_N$  is  $2f_{max}$  (1.2)

If this rule is violated, a problem called aliasing results.

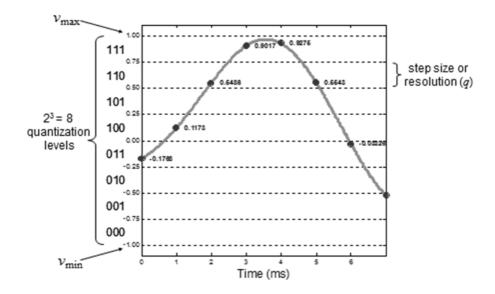

#### Quantizing

Quantization is the process of mapping the sampled analog voltages to discrete, binary levels. The number of bits determine the number of levels (1 bit is 2 levels, 2 bits is 4 levels, 2^n=#levels).

We determine the amplitudes associated with each sample point of an analog signal. We can then convert these amplitudes (real numbers) into binary numbers associated with their levels.

Quantizer is used that characterizes the length of the binary words they produce. An N-bit quantizer has  $2^N$  levels and outputs binary numbers of length N.

So, you might see:

Telephones use 8-bit encoding  $\rightarrow 2^8 = 256$  levels

CD audio uses 16-bit encoding  $\rightarrow 2^{16} = 65,536$  levels.

Figure 1.8. Quantized signal

Quantizers are limited to a specific voltage range. For the example above, we will assume that our analog input falls within a range of -1.0 to +1.0 volts.

The quantizer will partition this range into  $2^N$  steps of size q, the quantizer step size, given by

$$q = \frac{v_{\text{max}} - v_{\text{min}}}{2^N} \ . \tag{1.3}$$

So for the above example, step size will be

$$q = \frac{1 - (-1)}{8} = .25V. ag{1.4}$$

q, the step size, is formally called the <u>resolution</u>.

Each of the individual steps, called quantization intervals, is assigned a binary value from 0 to  $2^N - 1$ . So when you look at the above example, you can see our quantizer uses 3-bit encoding. This means the intervals will range from 0 to 7. So, 000 is assigned to the voltages from -0.75 to -1.0, 001 is assigned to the voltages from -0.5 to -0.74999..., and so on.

If sampled point falls within that interval (or bin), it is assigned that binary value. For the first sample point at time 0, the voltage is -0.1768, which means that sample is assigned a binary value of 011.

# **Digital signals**

Digital signals are more robust and easier to store and transport, that is why nowadays digital signals prevail.

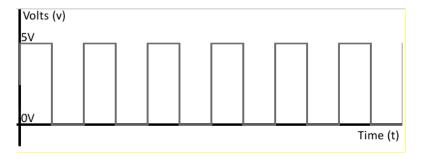

Digital signals must have a finite set of possible values. The number of values in the set can be anywhere between two and a-very-large-number-that's-not-infinity. Most commonly digital signals will be one of two values – like either 0V or 5V. Timing graphs of these signals look like square waves.

Figure 1.9. Timing graphs of a digital signal

A digital signal might be a discrete representation of an analogue waveform. Viewed from afar, the wave function below may seem smooth and analogue, but when you look closely there are tiny discrete **steps** as the signal tries to approximate values:

Figure 1.10. Digital signal as a discrete representation of an analogue waveform

That is the big difference between analog and digital waves. Analog waves are smooth and continuous, digital waves are stepping, square, and discrete.

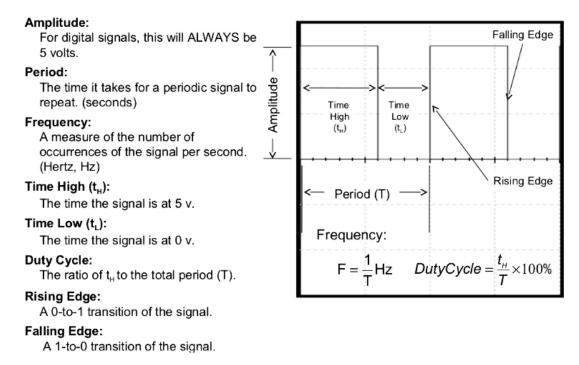

# Characteristics of a digital signal

Scientists and engineers often use a digitizer to capture analog data in the real world and convert it into digital signals for analysis. A digitizer is any device used to convert analog signals into digital signals. One of the most common digitizers is a cell phone, which converts a voice, an analog signal, into a digital signal to send to another phone. However, in test and measurement

applications, a digitizer most often refers to an oscilloscope or a digital multimeter (DMM). This article focuses on oscilloscopes, but most topics are also applicable to other digitizers.

Figure 1.11. Characteristics of a digital signal

Regardless of the type, the digitizer is vital for the system to accurately reconstruct a waveform. To ensure you select the correct oscilloscope for your application, consider the bandwidth, sampling rate, and resolution of the oscilloscope.

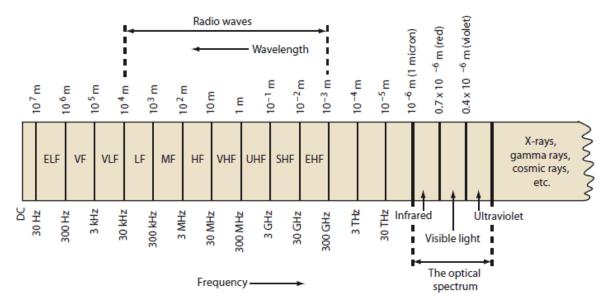

#### **Electromagnetic Spectrum**

A signal can be characterised by its behaviour over time or by its frequency components, which constitute its spectrum. Figure 1.11 gives you the big picture of the total spectrum from dc to light and beyond. Note both the frequency and wavelength measures. In the wireless world, we mainly use frequency. However, in the upper reaches of the spectrum, we use wavelength in meters as spectrum bands.

Figure 1.12 represents the entire electromagnetic spectrum. It goes all the way from very low frequency radio waves on the left, to very high frequency X-rays and gamma rays on the right.

In the middle, there is a very small region that represents visible light. In the scope of the entire electromagnetic spectrum, the range of frequencies that we can actually perceive with our eyes is very small. You can see on either side of visible light is infrared and ultraviolet.

But the area that we are interested in is the very narrow range of frequencies used by WiFi equipment. That is the very thin sliver at the low end of the microwave range.

<sup>1.</sup> The electromagnetic frequency spectrum ranges from dc to light. The lower radio frequencies are designated mainly by frequency. The optical ranges are referred to by wavelength.

Figure 1.12. Electromagnetic Spectrum

Electromagnetic (EM) communications with submarines are forced to use *very low EM* frequencies, because of the difficulties of propagation of higher frequency RF signals under water. Most of the other usages are concentrated on higher frequencies, because of the wider capacity available there (more channels and more data per channel). Examples are:

*Shortwaves* (international AM broadcast, maritime communications, radio amateurs HF bands, etc.): from 1 to 30 MHz

FM radio: from 88 to 108 MHz

*TV broadcast*: VHF channels in many bands from 40 to 250 MHz; UHF channels in many bands from 470 to 885 MHz (depending from the country)

*VHF and UHF radio ham* bands: around 140-150 and 440-450 MHz, together with many other users (services, security, police, etc...)

Mobile phones: 850, 900, 1800, 1900 and 2100 MHz for GSM and CDMA cellular networks;

GPS: 1227 and 1575 MHz

*Wi-Fi:* 2400-2485 MHz and 4915-5825 MHz (depending from the country). See http://en.wikipedia.org/wiki/List\_of\_WLAN\_channels for details.

*Radars:* common bands for radars are: L band (1–2 GHz), S band (2–4 GHz), C band (4–8 GHz), X band (8–12 GHz) but others are also used.

Satellite TV: C-band (4–8 GHz) and Ku-band (12–18 GHz)

*Microwave telecom links*: for example in the United States, the band 38.6 - 40.0 GHz is used for licensed high-speed microwave data links, and the 60 GHz band can be used for unlicensed

short range data links with data throughputs up to 2.5 Gbit/s. The 71-76, 81-86 and 92–95 GHz bands are also used for point-to-point high-bandwidth communication links.

The basic communication system is formed by a transmitter TX, a communication channel and a receiver RX.

The Transmitter injects a signal into the channel that delivers it to the receiver. The receiver must recover the information contained in the receiver signal despite the limitations introduced by the channel.

The channel can be a physical one, like a copper cable and an optical fibre, or simply air or even vacuum that transmits electromagnetic waves. Any channel is subject to some kind of electromagnetic "noise" and interference, will attenuate the signal and will change its shape (distortion).

Since it takes some time for the signal to traverse the channel, the received signal will have some latency with respect to the transmitted signal. This "latency" might change over time and contribute to "jitter" in the received signal.

The signal might also reach the receiver by means of different trajectories, and in this case, the different received versions will interact as a consequence of the "multipath". Multipath can completely obliterate a signal but it can also be used advantageously in some modern communications techniques. Although the effect of attenuation can easily be overcome with an amplifier, the amplifier will also enhance any noise introduced by the channel and inevitably introduce some extra noise of its own.

**The wavelength** (sometimes referred to as lambda,  $\lambda$ ) is the distance measured from a point on one wave to the equivalent part of the next, for example from the top of one peak to the next. The frequency is the number of whole waves that pass a fixed point in a period of time.

Waves also have a property called amplitude. This is the distance from the centre of the wave to the extreme of one of its peaks, and can be thought of as the "height" of a water wave.

Unlike waves in water, electromagnetic waves require no medium to carry them through space. It may be said that the media that oscillates is the electromagnetic field.

The phase of a wave is the fraction of a cycle that the wave is offset from a reference point. It is a relative measurement that can be express in different ways (radians, cycles, degrees, percentage). Two waves that have the same frequency and different phases have a phase difference, and the waves are said to be out of phase with each other.

Wavelength and Frequency:

$$c = f * \lambda \tag{1.5}$$

c = speed (meters / second)

f = frequency (cycles per second, or Hz)

$\lambda$  = wavelength (meters)

<u>Example</u>: If a wave on water travels at one meter per second, and it oscillates five times per second, then each wave will be twenty centimetres long:

1 meter/second = 5 cycles/second \*  $\lambda$

$\lambda = 1 / 5$  meters

$\lambda = 0.2 \text{ meters} = 20 \text{ cm}$

A wave has a certain speed, frequency, and wavelength. These are connected by a simple relation: Speed = Frequency \* Wavelength

The wavelength (sometimes referred to as lambda,  $\lambda$ ) is the distance measured from a point on one wave to the equivalent part of the next, for example from the top of one peak to the next. The frequency is the number of whole waves that pass a fixed point in a period of time. Speed is measured in meters/second, frequency is measured in cycles per second (or Hertz, abbreviated Hz), and wavelength is measured in meters.

#### **Bandwidth**

The bandwidth of a composite signal is the difference between the highest and the lowest frequencies contained in that signal.

Typically, the bandwidth of a filter is specified in terms of 3db (half-power) bandwidth -for a given transfer function, bandwidth spans the frequency range where the magnitude is greater than 3dB down from maximum gain. It can be easily measured by driving the circuit with a sinusoidal source and monitoring output level.

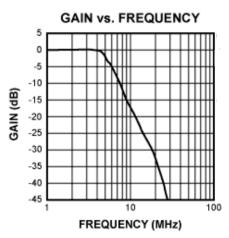

Figure 1.13. Gain versus frequency

Bandwidth is measured between the lower and upper frequency points where the signal amplitude falls to -3 dB below the passband frequency. This sounds complicated, but when you break it down it is actually relatively easy.

First, calculate -3 dB value.

$$-3 dB = 20 \log \frac{V_{out,pp}}{V_{in,pp}}$$

$$\tag{1.6}$$

$V_{in,pp}$  is the peak-to-peak voltage of the input signal and  $V_{out,pp}$  is the peak-to-peak voltage of the output signal. For example, if you input a 1 V sine wave, the output voltage can be calculated

as

$$-3 = 20 \log \frac{V_{out,pp}}{1}$$

so  $V_{out,pp} \approx 0.7 V$ .

Because the input signal is a sine wave, there are two frequencies at which the output signal hits this voltage; these are called the corner frequencies  $f_1$  and  $f_2$ . These two frequencies go by many different names such as corner frequency, cut-off frequency, crossover frequency, half-power frequency, 3 dB frequency, and break frequency. However, all these terms refer to the same values. The center frequency,  $f_0$ , of the signal is the geometric mean of  $f_1$  and  $f_2$ .

$$f_o = \sqrt{f_1 f_2} \tag{1.7}$$

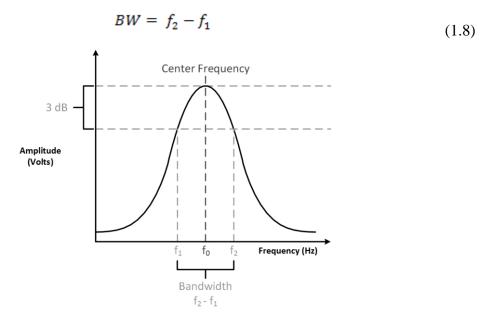

Calculate the bandwidth (BW) by subtracting the two corner frequencies.

Figure 1.14. The bandwidth, the corner frequency, the center frequency, and the 3 dB point

# Example:

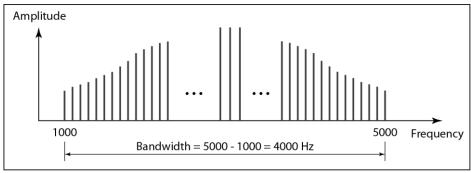

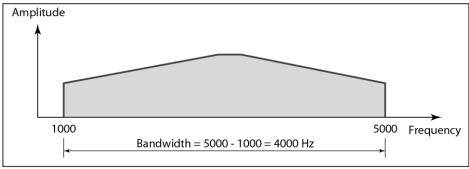

a. Bandwidth of a periodic signal

b. Bandwidth of a nonperiodic signal

Figure 1.15. Bandwidth of a periodic and a non-periodic signals

# **Spectrum**

Spectrum is:

- A signal is a function of time which can be represented by a series of sinusoidal functions or sinusoidal components.

- These sinusoidal components have different frequencies, different amplitudes, and different phases.

- Therefore, the plots of frequency versus amplitude and phase for the sinusoidal components which comprise the signal are called the Frequency Spectrum or Spectrum of the signal.

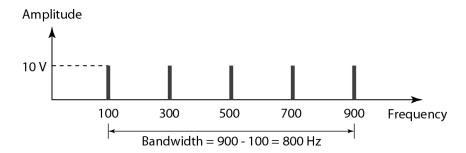

<u>Example</u>: If a periodic signal is decomposed into five sine waves with frequencies of 100, 300, 500, 700, and 900 Hz, what is its bandwidth? Draw the spectrum, assuming all components have a maximum amplitude of 10 V.

Solution: Let  $f_h$  be the highest frequency,  $f_l$  the lowest frequency, and B the bandwidth. Then  $= f_h - f_l = 900 - 100 = 800 Hz$ . The spectrum has only five spikes, at 100, 300, 500, 700, and 900 Hz.

Figure 1.16. The spectrum of a periodic signal

# Noise

Noise is a typical random signal, described by its mean power and frequency distribution.

Pure signal, e.g. put into one end of the phone

Figure 1.17. Pure signal

Signal + noise as it comes out of the other end of the phone

Figure 1.18. Signal + noise

What do "errors" look like in an analog system? The signal you care about is translated from sound to electricity and so on. With each translation step, little errors creep in. The microphone has a little stiffness, the wires don't carry the signal perfectly, and so on. The errors are called "noise" -- you can imagine the pure sound signal you wanted but it's been distorted by little up/down errors -- like fuzzy variations around the true signal.

#### Interference

Radio-frequency interference (RFI) when in the radio frequency spectrum, is a disturbance generated by an external source that affects an electrical circuit by electromagnetic induction, electrostatic coupling, or conduction.

In unlicensed bands (e.g., 802.11), there are lots of transmitters - 802.11 cards - 802.15.1 (Bluetooth) - 802.15.4 (ZigBee) - 2.4GHz phones - Microwave ovens

This interference can be stronger or weaker than the signal, and can prevent successful reception.

#### Sources of EMI

EMI sources, both natural and man-made, that compose the EME can be categorized into several primary categories. Some of these classifications of sources are listed below.

- (1) Ambient EME that is composed of numerous sources of which the most significant are:

- Television transmissions both analogue and digital.

- Radio AM, FM, and Satellite.

- Solar Magnetic Storms which peak on a eleven year cycle.

- Lightning which occurs as a very high voltage and high current event.

- Utility power grid transmission lines which have high voltage, low current, and low frequency characteristics. In this category is also the new technology of Broadband over Power Lines (BPL) digital signals.

- Other ambient EME sources include airport port radar, telecom transmissions, electrostatic discharge (ESD), and white noise. Also in this category is the earth's magnetic field flux, which has a value of about 500 milligauss.

- Some other major product and system's emissions sources include switching mode power supplies, arc welders, motor bushes, and electrical contacts.

- (2) High Powered Electromagnetic Pulse (HEMP) threats which are intended to disable electrical and electronic equipment. These sources are designed to be utilized by terrorist and military organizations. Currently existing HEMP devices include the following:

- Intentional Electromagnetic Interference (IEMI) source a high powered pulse device utilized by combat, sabotage and terrorist organizations.

- High Altitude Nuclear Electromagnetic Pulse (HNEMP) produced by the detonation of a nuclear device high above the earth's atmosphere.

- High Powered Microwave Weapon (HPM) a device utilized by the military as a combat weapon.

- E-Bomb a HEMP weapon employed by the military to disrupt an enemy's intra structure that is delivered by an aircraft.

- EMP Cannon a military tactical weapon.

- (3) Power Quality degradation1 factors can effect the operation of equipment that is powered by a mains power source. These mains degradation factors include:

- Voltage surges, sages, dips, spikes, and high and low voltage.

- Brownouts and blackouts.

- Power line faults.

- Electrical Fast Transitions (EFT).

- Electrical noise superimposed on the mains power line.

These power quality degradation factors can occur simultaneously or independently, during any time interval.

- (4) Railroad and Mass Transit Systems have some unique types of EMI source problems. These include:

- Propulsion system's high voltage and high current operational mode emissions.

- Train signalling systems and their associated computer operating codes.

- Third rail shoes arcing broadband emissions.

- High voltage contact switching arcing broadband emissions.

- Train control system's emissions.

- Track train control circuits.

- Right away emission sources.

- (5) Medical equipment utilized in medical facilities has numerous EMI sources. Some of the more prominent of these are listed below:

- Life support equipment such as ventilators, cardiac defibrillators, infusion pumps, etc.

- Patient telemetry and assistance equipment which includes electrocardiographs and motorized wheelchairs.

- Electrical surgical units and their associated support equipment.

- Magnetic Resonance Imagine (MRIs) systems.

- X-ray units, both therapeutic and diagnostic.

- Gamma Beam Electron Accelerators and Therapeutic equipment.

#### Sources and their most significant effects

(1) Ambient (EME) – Can affect sensitive electronic equipment in the vicinity of the EMI sources. The closer the sensitive electronic equipment is to the EMI source, the higher the source's radiated power level, and its in-band frequency the greater is the probability that the EMI will cause an interference problem.

In the case of the effects of ESD on sensitive electronic systems it can cause upsets, burn outs, and latch-ups in these units.

(2) High Powered Electromagnetic Pulse effects – High powered electromagnetic sources can totally destroy an electrical and electronic equipment's function.

As an example, an HNEMP device detonation above the earth's atmosphere of the United States can totally immobilize the whole of the continental United States' infrastructure. IEMI, HPM, E-Bombs, and EMP Cannons can be utilized to disable electronic systems at specific locations.

- (3) Power Quality distortions and transits that are present on the power main systems can affect the normal operation of the equipment that it supplies power. Transits such as power surges are capable of destroying interface electronic circuits. EFTs can cause electronic circuit upset conditions.

- (4) Railroad and Mass Transit Systems have one primary source of EMI and that is the transit and railroad engine's propulsion systems, which operates with high voltages, currents, and magnetic field levels. They have been known to affect other facilities that contain sensitive electrical equipment that are located near the railroad or mass transit systems right away. These propulsion systems have had EMI associated problems with other elements of their systems. Train control electronics can be affected by EMI sources such as third rail and other broadband frequency arcing sources if they are not adequate designed for EMC.

- (5) Medical equipment and facilities sources include patient monitoring systems

Those are very susceptible to EMI interactions. The human body signals that they monitor are very weak. They are measured in unites of microvolts and micro-amps. Among other devices that are susceptible to EMI are hearing aids, wireless patient monitoring systems, magnetic resonance imaging systems, implantable cardiovascular devices, drug pumps, and portable diagnostic meters. As new technologies are developed and enter the marketplace at a fast pace the list will grow.

## Signal to Interference-and-Noise Ratio (SINR)

Measured in dB:|S|/|(N+I)|

- S = -50 dBm, N+I = -95 dBm, SINR = 35 dB

- S = -89 dBm, N+I = -93 dBm, SINR = 4 dB

#### **Channel capacity**

The channel capacity determines the maximum transmission rate that a wireless channel can sustain with a negligible error probability in terms of bits per second per unit bandwidth. For the case of an ideal channel, where the only impairment in the wireless channel is the introduction of additive white Gaussian noise (AWGN), the channel capacity is given by Shannon's well-known formula.

$$C = \log_2(1+\gamma) \text{ (bits/s/Hz)}$$

(1.9)

where  $\gamma$  is the ratio of the received signal power to the AWGN power, also known as the received signal-to-noise ratio (SNR). The consequence of Shannon's mathematical construct was the Shannon coding theorem and its converse. The Shannon coding theorem proves that there exists a code, which if utilized, allows to transmit data without errors at a rate r (bits/s/Hz) as long as r < C. While, the converse theorem showed that the error probability is always larger than zero if the transmission rate r is higher than the capacity C.

The channel capacity formula in (1.5) considers a simple scenario, by assuming an ideal AWGN channel. However, a realistic description of wireless propagation environment is far more complex. Mobile fading channels, particularly in urban environments, are generally classified as time-variant multipath fading channels, which can well be characterized with the help of proper statistical channel models.

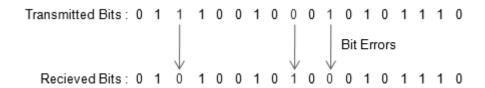

#### **Bit Error Rates (BER)**

The ultimate measure of quality in digital transmission is the *BER* -*Bit Error Rate* that corresponds to the fraction of erroneously decoded bits. Typical values of BER range between  $10^{-3}$  and  $10^{-9}$ .

On the surface, BER is a simple concept—its definition is simply:

BER = Errors/Total Number of Bits.

If the received bit is different from the transmitted bit, it is said that the data has bit error. As an example, if you have the transmitted bit stream and received bit stream as shown below, we can say this bit stream (data stream) has 3 bit errors. You see there are three locations where the transmitted bit and received bit is different.

It is the ratio of the number of bit errors and the total number of transmitted bits. It would be clear if you have a simple example as follows.

#### Example:

A million bits  $(10^6)$  was transmitted and 243 bits were found to be errors at the receiver. What is the bit error rate?

Solution: Bit Error Rate = (Number of Error Bits)/(Number of Transmitted Bits) =  $243/10^6$  =  $2.43 \times 10^{-4}$ .

Figure 1.19. BER: Bit Error Rate

#### **Modulation**

Modulation is the process of superimposing the information contents of a modulating signal on a carrier signal (which is of high frequency) by varying the characteristic of carrier signal according to the modulating signal.

The robustness of the digital signal is also exemplified by the fact that it was chosen for the first trials of radio transmission. Marconi showed the feasibility of long distance transmission, but pretty soon realised that there was a need to share the medium among different users.

This was achieved by assigning different carrier frequencies which were modulated by each user's message. Modulation is a scheme to modify the amplitude, frequency or phase of the carrier according with the information one wants to transmit. The original information is retrieved at destination by the corresponding demodulation of the received signal.

These modulation techniques are classified into two major types: analog and digital or pulse modulation. Prior to discussing further about the different types of modulation techniques, let us understand the importance of modulation.

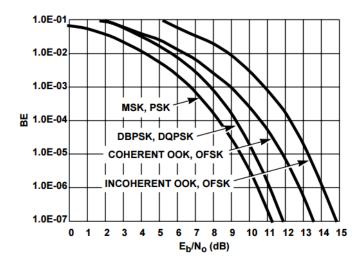

The combination of different modulation schemes has resulted in a plethora of modulation techniques depending on which aspect one wants to optimise: robustness against noise, amount of information transmitted per second (capacity of the link in bits/second) or spectral efficiency (number of bits/s per Hertz).

For instance, BPSK -Binary Phase Shift Keying- is a very robust modulation technique but transmits only one bit per symbol, while 256 QAM -Quaternary Amplitude Modulation- will

carry 8 bits per symbol, thus multiplying by a factor of eight the amount of information transmitted per second, but to correctly distinguish amongst the 256 symbols transmitted, the received signal must be very strong as compared with the noise (a very high S/N -Signal/Noise ratio- is required).

The modulation also allows us to choose which range of frequency we want to use for a given transmission. All frequencies are not created equal and the choice of the carrier frequency is determined by legal, commercial and technical constraints.

# **Analog Modulation**

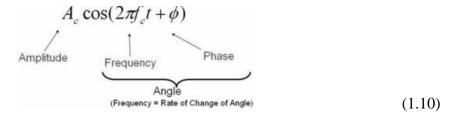

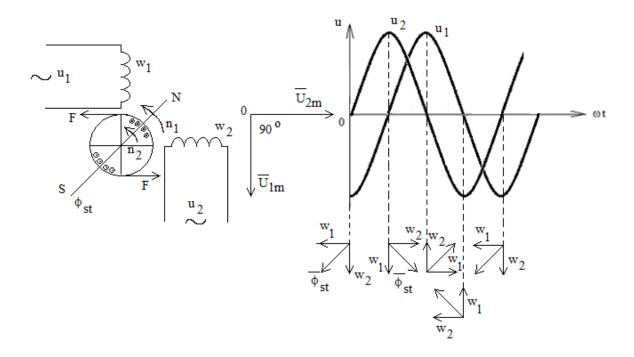

In this modulation, a continuously varying sine wave is used as a carrier wave that modulates the message signal or data signal. The Sinusoidal wave's general function is shown in the figure below, in which, three parameters can be altered to get modulation – they are amplitude, frequency and phase, so the types of analog modulation are:

- Amplitude modulation (AM)

- Frequency modulation (FM)

- Phase modulation (PM)

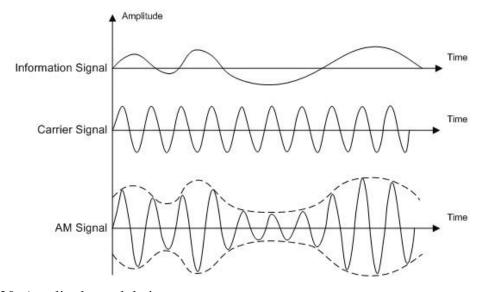

In amplitude modulation, the amplitude of the carrier wave is varied in proportion to the message signal, and the other factors like frequency and phase remain constant. The modulated signal is shown in the below figure, and its spectrum consists of lower frequency band, upper frequency band and carrier frequency components. This type of modulation requires greater band width, more power. Filtering is very difficult in this modulation.

Figure 1.20. Amplitude modulation

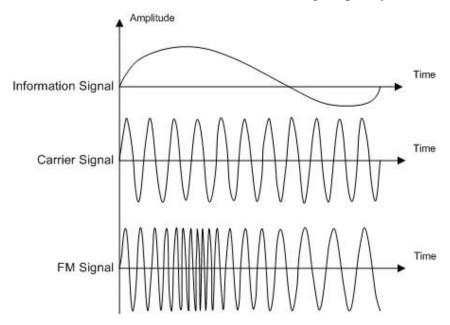

**Frequency modulation** (FM) varies the frequency of the carrier in proportion to the message or data signal while maintaining other parameters constant. The advantage of FM over AM is the greater suppression of noise at the expense of bandwidth in FM. It is used in applications like radio, radar, telemetry seismic prospecting, and so on. The efficiency and bandwidths depend on modulation index and maximum modulating frequency.

Figure 1.21. Frequency modulation

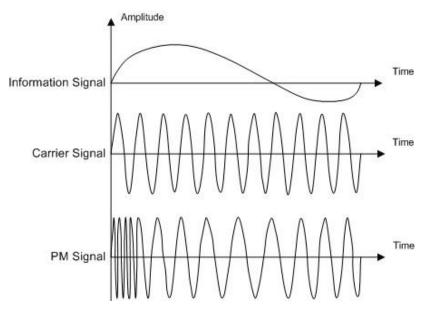

Phase modulation, the carrier phase is varied in accordance with the data signal. In this type of modulation, when the phase is changed it also affects the frequency, so this modulation also comes under frequency modulation.

Analog modulation (AM, FM and PM) is more sensitive to noise. If noise enters into a system, it persists and gets carried till the end receiver. Therefore, this drawback can be overcome by the digital modulation technique.

Figure 1.22. Phase modulation

#### **Digital Modulation**

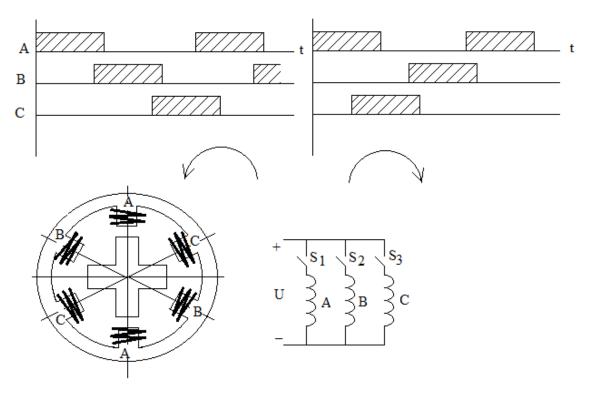

For a better quality and efficient communication, digital modulation technique is employed. The main advantages of the digital modulation over analog modulation include permissible power, available bandwidth and high noise immunity. In digital modulation, a message signal is converted from analog to digital message, and then modulated by using a carrier wave.

The carrier wave is keyed or switched on and off to create pulses such that the signal is modulated. Similar to the analog, here the parameters like amplitude, frequency and phase variation of the carrier wave decides the type of digital modulation.

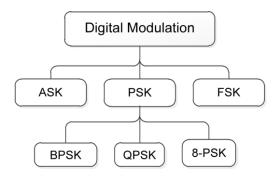

Figure 1.23. Types of Digital Modulation

Digital modulation is of several types depending on the type of signal and application used such as Amplitude Shift Keying, Frequency Shift Keying, Phase Shift Keying, Differential Phase Shift Keying, Quadrature Phase Shift Keying, Minimum Shift Keying, Gaussian Minimum Shift Keying, Orthogonal Frequency Division Multiplexing, etc., as shown in the figure.

Amplitude shift keying changes the amplitude of the carrier wave based on the base band signal or message signal, which is in digital format. It is used for low-band requirements and is sensitive to noise.

In frequency shift keying, the frequency of the carrier wave is varied for each symbol in the digital data. It needs larger bandwidths as shown in the figure. Similarly, the phase shift keying changes the phase of the carrier for each symbol and it is less sensitive to noise.

# **Multiplexing**

Multiplexing is the sharing of a single communication channel among different users. The communication channel can be a copper wire, an optical fiber or the space between a transmitting and a receiving antenna.

Different users can be distinguished by means of different frequencies, time slots, codes or regions of space.

The process of making the most effective use of the available channel capacity is called Multiplexing. For efficiency, the channel capacity can be shared among a number of communicating stations just like a large water pipe can carry water to several separate houses

at once. Most common use of multiplexing is in long-haul communication using coaxial cable, microwave and optical fibre.

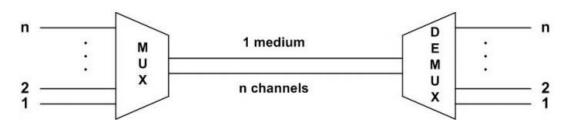

The multiplexer is connected to the demultiplexer by a single data link. The multiplexer combines (multiplexes) data from these 'n' input lines and transmits them through the high capacity data link, which is being demultiplexed at the other end and is delivered to the appropriate output lines. Thus, Multiplexing can also be defined as a technique that allows simultaneous transmission of multiple signals across a single data link.

Figure 1.24. Basic concept of multiplexing

#### **Multiplexing techniques**

In FDMA (Frequency Division Multiple Access), each user has a different frequency band allocated. In frequency division multiplexing, the available bandwidth of a single physical medium is subdivided into several independent frequency channels. Independent message signals are translated into different frequency bands using modulation techniques, which are combined by a linear summing circuit in the multiplexer, to a composite signal. The resulting signal is then transmitted along the single channel by electromagnetic means as shown in Fig. 1.25.

Figure 1.25. Basic concept of FDM

Basic approach is to divide the available bandwidth of a single physical medium into a number of smaller, independent frequency channels. Using modulation, independent message signals are translated into different frequency bands. All the modulated signals are combined in a linear summing circuit to form a composite signal for transmission.

In TDMA (Time Division Multiple Access), each user has d different time slot allocated, while the same frequency is shared among all the users of the service.

In frequency division multiplexing, all signals operate at the same time with different frequencies, but in Time-division multiplexing all signals operate with same frequency at different times. This is a base band transmission system, where an electronic commutator sequentially samples all data source and combines them to form a composite base band signal,

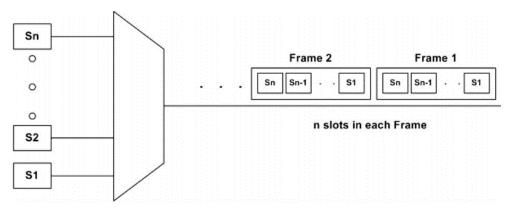

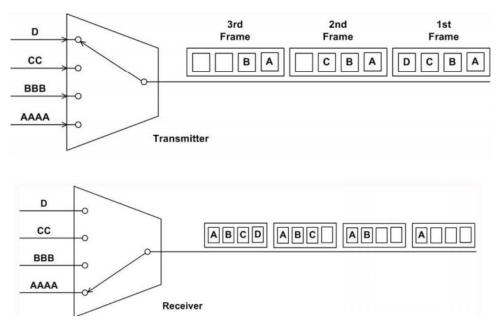

which travels through the media and is being demultiplexed into appropriate independent message signals by the corresponding commutator at the receiving end. The incoming data from each source are briefly buffered. Each buffer is typically one bit or one character in length. The buffers are scanned sequentially to form a composite data stream. The scan operation is sufficiently rapid so that each buffer is emptied before more data can arrive. Composite data rate must be at least equal to the sum of the individual data rates. The composite signal can be transmitted directly or through a modem. The multiplexing operation is shown in Fig. 1.26.

Figure 1.26. Time division multiplexing operation

As shown in the Fig 1.26. the composite signal has some dead space between the successive sampled pulses, which is essential to prevent inter channel cross talks. Along with the sampled pulses, one synchronizing pulse is sent in each cycle. These data pulses along with the control information form a frame. Each of these frames contain a cycle of time slots and in each frame, one or more slots are dedicated to each data source. The maximum bandwidth (data rate) of a TDM system should be at least equal to the same data rate of the sources. Synchronous TDM is called synchronous mainly because each time slot is preassigned to a fixed source. The time slots are transmitted irrespective of whether the sources have any data to send or not. Hence, for the sake of simplicity of implementation, channel capacity is wasted. Although fixed assignment is used TDM, devices can handle sources of different data rates. This is done by assigning fewer slots per cycle to the slower input devices than the faster devices. Both multiplexing and demultiplexing operation for synchronous TDM are shown in Fig. 1.27.

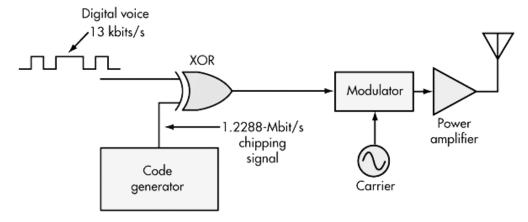

IN CDMA (Code Division Multiple Access), the users are distinguished by means of a special mathematical code, while sharing the same frequency and time slots. CDMA is also known as spread spectrum because it takes the digitized version of an analogue signal and spreads it out over a wider bandwidth at a lower power level. This method is called direct sequence spread spectrum (DSSS) as well (Fig. 1.28). The digitized and compressed voice signal in serial data form is spread by processing it in an XOR circuit along with a chipping signal at a much higher frequency. In the cdma IS-95 standard, a 1.2288-Mbit/s chipping signal spreads the digitized compressed voice at 13 kbits/s.

Figure 1.27. Multiplexing and demultiplexing in synchronous TDM

Figure 1.28. Spread spectrum is the technique of CDMA

The chipping signal is derived from a pseudorandom code generator that assigns a unique code to each user of the channel. This code spreads the voice signal over a bandwidth of 1.25 MHz. The resulting signal is at a low power level and appears more like noise. Many such signals can occupy the same channel simultaneously. For example, using 64 unique chipping codes allows up to 64 users to occupy the same 1.25-MHz channel at the same time. At the receiver, a correlating circuit finds and identifies a specific caller's code and recovers it.

The third generation (3G) cell-phone technology called wideband CDMA (WCDMA) uses a similar method with compressed voice and 3.84-Mbit/s chipping codes in a 5-MHz channel to allow multiple users to share the same band.

# **IN OFDM (Orthogonal Frequency Division Multiplexing)**

OFDM is a transmission technique that has been around for years, but only recently became popular due to the development of digital signal processors (DSPs) that can handle its heavy digital processing requirements.

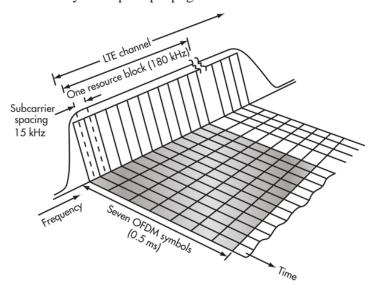

Orthogonal frequency division multiplexing (OFDM) is a modulation method that divides a channel into multiple narrow orthogonal bands that are spaced so they do not interfere with one another. Each band is divided into hundreds or even thousands of 15-kHz wide subcarriers.

The data to be transmitted is divided into many lower-speed bit streams and modulated onto the subcarriers. Time slots within each subchannel data stream are used to package the data to be transmitted (Fig. 1.29). This technique is very spectrally efficient, so it provides very high data rates. It also is less affected by multipath propagation effects.

Figure 1.29. OFDMA assigns a group of subcarriers to each user

To implement OFDMA, each user is assigned a group of sub channels and related time slots. The smallest group of sub channels assigned is 12 and called a resource block (RB). The system assigns the number of RBs to each user as needed.

#### Behaviour of radio waves

There are a few simple rules of thumb that can prove extremely useful when making first plans for a wireless network:

- The longer the wavelength, the further it goes

- The longer the wavelength, the better it travels through and around things

- The shorter the wavelength, the more data it can transport

Assuming equal power levels, waves with longer wavelengths tend to travel further than waves with shorter wavelengths. Lower frequency transmitters can reach greater distances than high frequency transmitters at the same power.

It is harder to visualize waves moving "through" solid objects, but this is the case with electromagnetic waves. Longer wavelength (and therefore lower frequency) waves tend to penetrate objects better than shorter wavelength (and therefore higher frequency) waves. For example, FM radio (88-108MHz) can travel through buildings and other obstacles easily, while shorter waves (such as GSM phones operating at 900MHz or 1800MHz) have a harder time penetrating buildings. This effect is partly due to the difference in power levels used for FM radio and GSM, but is also partly due to the shorter wavelength of GSM signals.

## **Absorption**

When electromagnetic waves go through some material, they generally get weakened or dampened. Materials that absorb energy include:

- Metal. Electrons can move freely in metals, and are readily able to swing and thus absorb the energy of a passing wave.

- Water molecules jostle around in the presence of radio waves, thus absorbing some energy.

- Trees and wood absorb radio energy proportionally to the amount of water contained in them.

- Humans are mostly water: we absorb radio energy quite well!

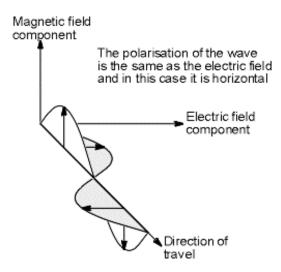

### **Polarization**

- Electromagnetic waves have *electrical* and *magnetic components* that oscillate perpendicular to each other and to the direction of the propagation.

- The *polarization* of the wave corresponds to the plane in which the electrical oscillations occur.

Another important quality of electromagnetic waves is polarization. Polarization describes the direction of the electrical field vector. If you imagine a vertically aligned dipole antenna (a straight piece of wire), electrons only move up and down, not sideways (because there is no room to move) and thus electrical fields only ever point up or down, vertically. The energy leaving the wire and traveling as a wave has a strict linear (and in this case, vertical) polarization. If we put the antenna flat on the ground, we would find horizontal linear polarization.

Most Wi-Fi antennas we work with are linearly polarized, but circularly polarized antennas are also sometimes used (for special purposes). The polarization of a transmitting and receiving antenna MUST MATCH for optimum communications.

Figure 1.30. The polarization of the wave

#### **Conclusions**

- The communication system must overcome the noise and interference to deliver the signal to the receiver.

- The capacity of the communication channel is proportional to the bandwidth and to the logarithm of the S/N ratio.

- Modulation is used to adapt the signal to the channel and to allow several signals to share the same channel.

- Higher order modulation schemes allows for a higher transmission rate, but require higher S/N ratio

- The channel can be shared by several uses that occupy different frequencies, different time slots or different codes,

- Radio waves have a characteristic wavelength, frequency and amplitude, which affect the way they travel through space.

- Wi-Fi uses a tiny part of the electromagnetic spectrum. Lower frequencies travel further, but at the expense of throughput.

- Radio waves occupy a volume in space, the Fresnel zone, which should be unobstructed for optimum reception.

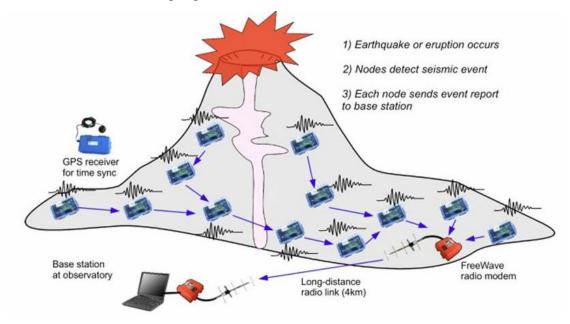

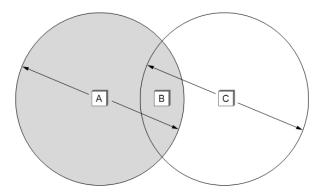

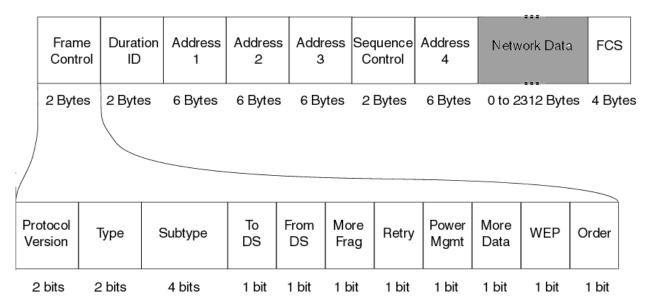

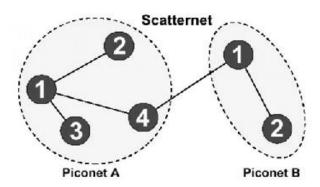

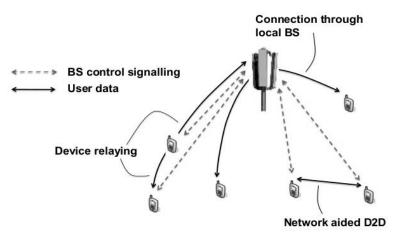

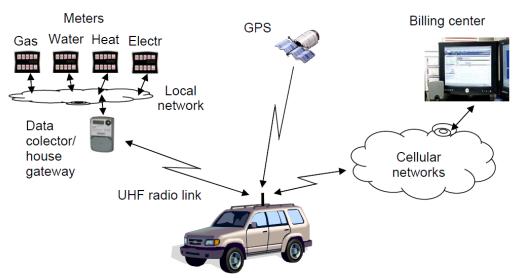

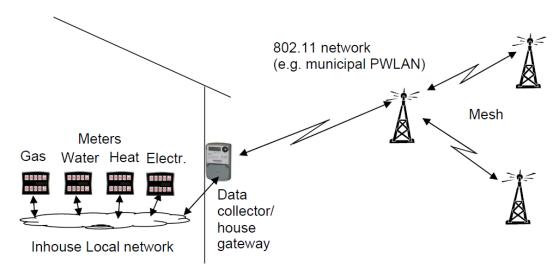

# 1.1.3. Wireless sensor networks in smart metering

Wireless network today refers to any kind of communication that can be implemented without wires, such as wireless energy transfer and wireless remote control. Automatic detection, prevention, and recovery from urban disasters are one of many potentials uses for wireless sensor networks. Despite their variety, all sensor networks have certain fundamental features in common. Sensors detect the world's physical nature, such as light intensity, temperature, sound, or proximity to objects. Similarly, actuators, affect the world in some way, such as toggling a

switch, making a noise, or exerting a force. Sensors perform monitoring and remote diagnostics, and they usually use battery-powered transceivers.

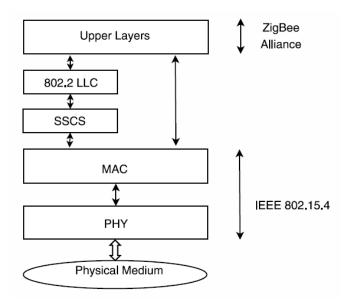

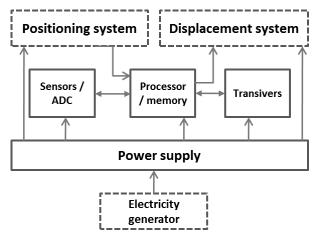

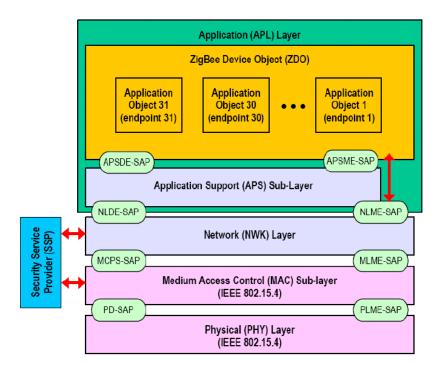

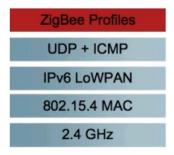

A Wireless sensor network (WSN) consists of wireless sensor nodes or motes, which are devices equipped with a processor, a radio interface, an analogue-to-digital converter, sensors, memory, and a power supply. The processor provides the mote management functions and performs data processing. The sensors attached to the mote are capable of sensing temperature, humidity, light, etc. Due to bandwidth and power constraints, motes primarily support low data units with limited computational power and a limited sensing rate. Memory is used to store programs (instructions executed by the processor) and data (raw and processed sensor measurements). Motes are equipped with a low-rate (10–100 kbps) and short-range (less than 100 m) wireless radio, e.g., IEEE 802.15.4 radio to communicate among themselves. Since radio communication consumes most of the power, the radio must incorporate energy-efficient communication techniques. The power source commonly used is rechargeable batteries (P. Rawat, K. D. Singh, H. Chaouchi, J. M. Bonnin, 2013).

Since motes can be deployed in remote and hostile environments they must use little power and must employ built-in mechanisms to extend network lifetime. For example, motes may be equipped with effective power harvesting methods, such as solar cells, so they may be left unattended for years.

Sensor nodes can be deployed in an ad-hoc or a pre-planned manner. An ad-hoc deployment is good for large uncovered regions where a network of a very large number of nodes can be deployed and left unattended to perform monitoring and reporting functions. Network maintenance such as managing connectivity and detecting failures is difficult in such a WSN due to large number of nodes. On the other hand, preplanned deployment is good for limited coverage where fewer nodes are deployed at specific locations with the advantage of lower network maintenance and management cost.

### **WSN:** challenges and requirements

The collaborative nature of WSNs brings several advantages over conventional wireless ad-hoc networks, including self-organization, rapid deployment, flexibility, and inherent intelligent-processing capability. However, the unique features of WSN present new challenges in hardware design, communication protocols, and application design. A WSN technology must address these challenges to realize the numerous envisioned applications. This requires modifying legacy protocols for conventional wireless ad-hoc networks or designing new effective communication protocols and algorithms (Rodrigues J.J., Neves P.A., 2010)

Table 1. Challenges vs. required mechanisms in WSN (P. Rawat, K. D. Singh, H. Chaouchi, J. M. Bonnin, 2013)

| Challenges           | Required mechanisms        |

|----------------------|----------------------------|

| Resource constraints | Efficient use of resources |

| Dynamic and extreme environment                | Adaptive network operation                                                 |  |

|------------------------------------------------|----------------------------------------------------------------------------|--|

| conditions                                     |                                                                            |  |

| Data redundancy                                | Data fusion and localized processing                                       |  |

| Unreliable wireless communication              | Reliability                                                                |  |

| No global identification (ID) for sensor nodes | Data-centric communication paradigm                                        |  |

| Prone to node failures                         | Fault tolerance                                                            |  |

| Large scale deployment                         | Low-cost small-sized sensors with self-configuration and self-organization |  |

Table 1 lists important challenges and corresponding required mechanisms to address them in WSN. Sensor nodes have resource constraints including limited energy, limited memory, and computational capacities. The limited energy supplies of the sensor nodes in the network impose lifetime constraints on the WSN. The problem of limited resources can be addressed by using them efficiently.

Dynamic network topologies and harsh environment conditions may cause sensor node failures and performance degradation. This requires WSN to support adaptive network operation including adaptive signal-processing algorithms and communication protocols to enable endusers to cope with dynamic wireless-channel conditions and varying connectivity.

The communication in WSN is unreliable due to error prone wireless medium with high bit error rates and variable-link capacity. Thus, a WSN should be reliable in order to function properly and depending on the application requirements, the sensed data should be reliably delivered to the sink node. WSNs are usually prone to unexpected node failures due to different reasons like nodes may run out of energy or might be damaged (in extreme environment conditions), or wireless communication between two nodes can be permanently interrupted. This requires WSNs to be robust to node failures. In WSN, fault tolerance can be improved through a high level of redundancy by deploying additional nodes than required if all nodes functioned properly.

Since WSNs may contain a large number of sensor nodes, the employed architectures and protocols must be able to scale to sizes of thousands or more. Moreover, a large scale deployment of WSN requires low-cost and small-sized sensor nodes. A WSN should be able to self-organize itself as the network topology may change due to reasons like node failure, mobility, and large scale deployments.

## Types of WSNs

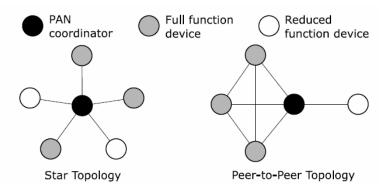

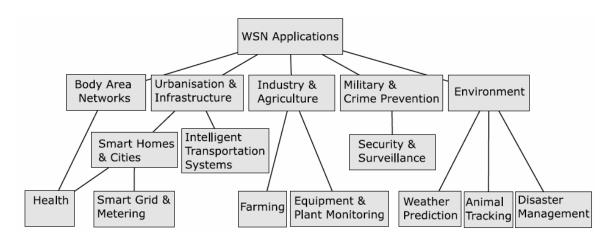

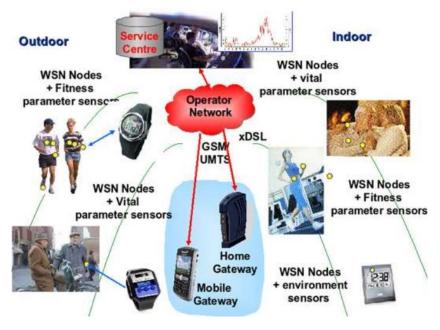

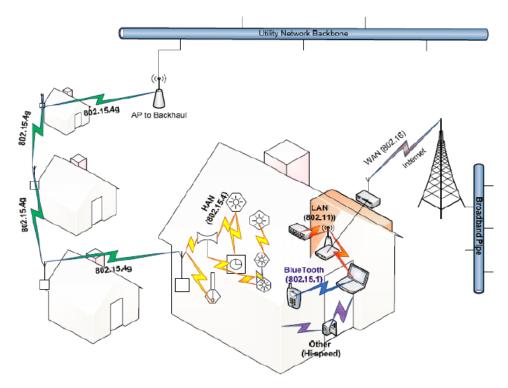

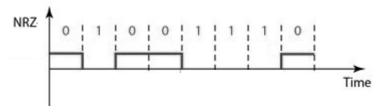

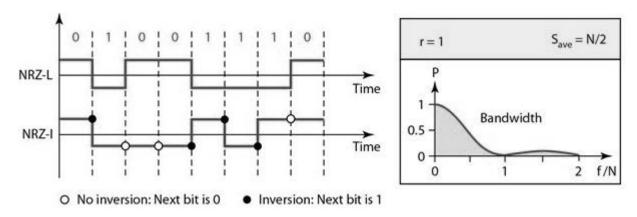

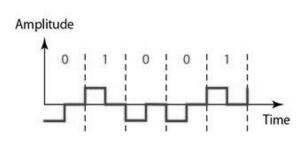

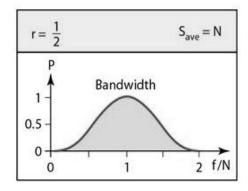

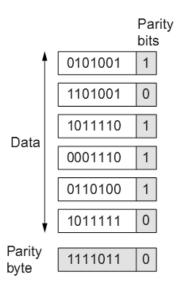

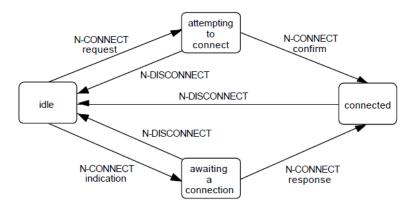

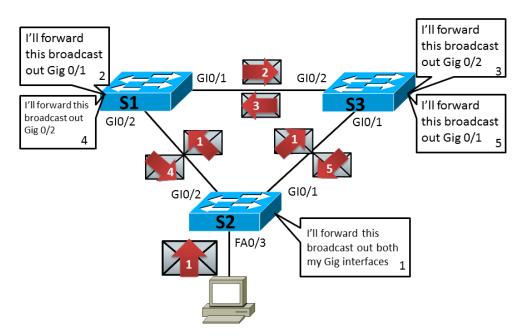

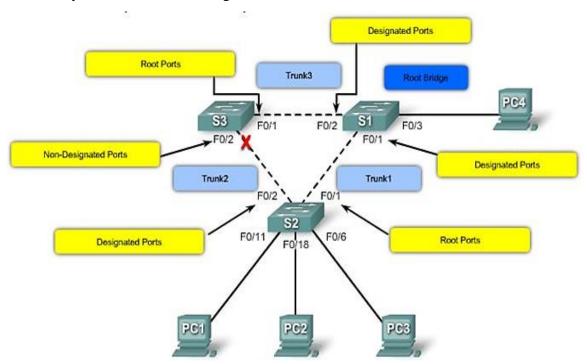

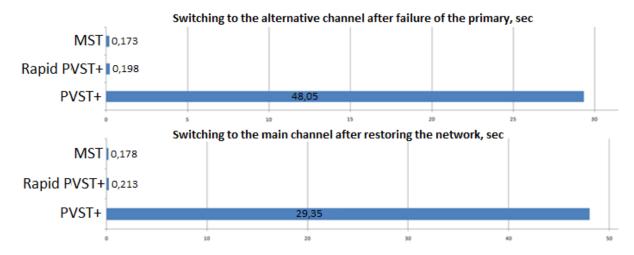

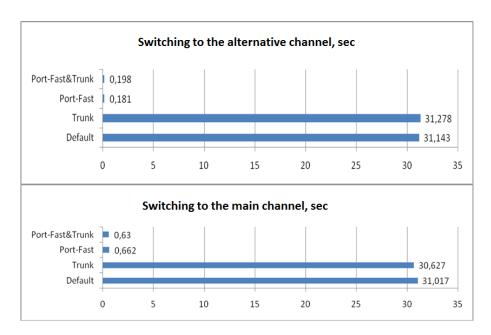

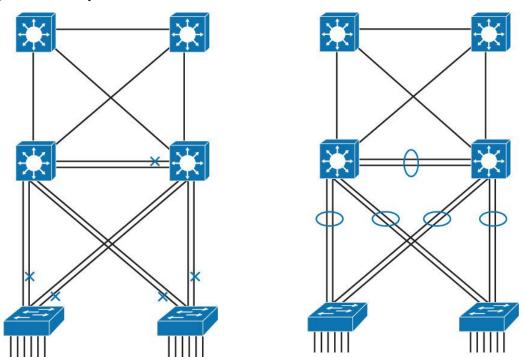

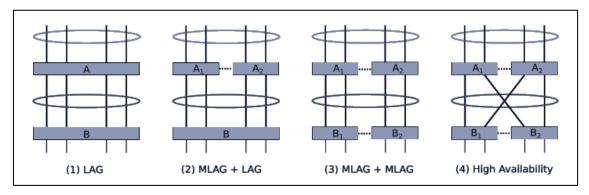

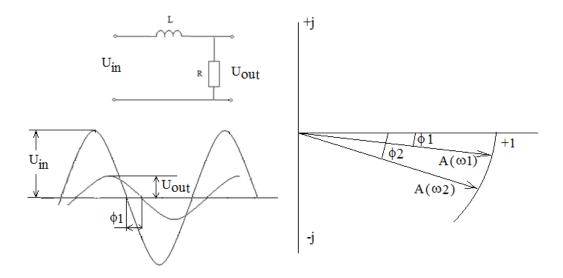

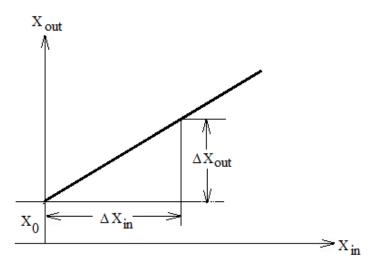

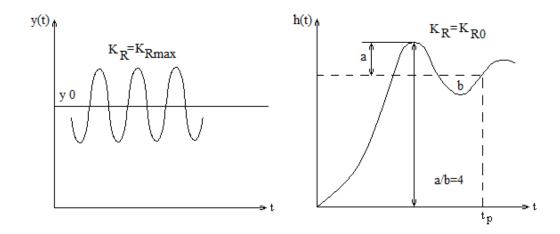

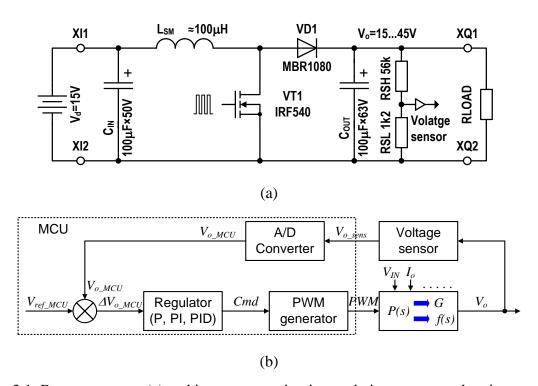

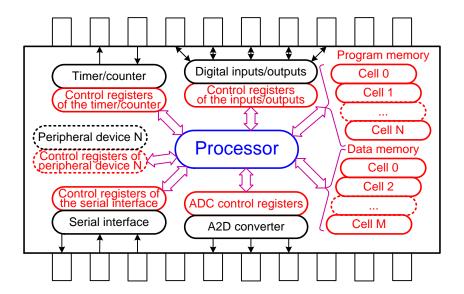

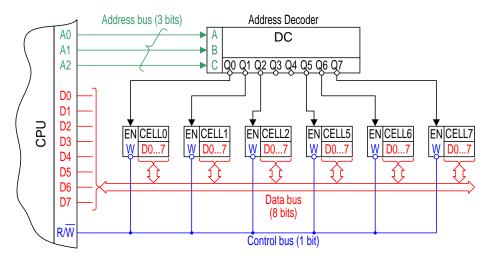

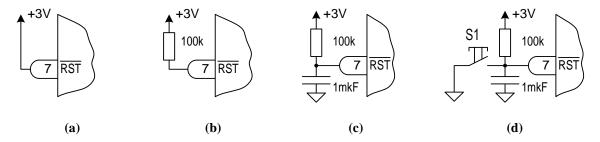

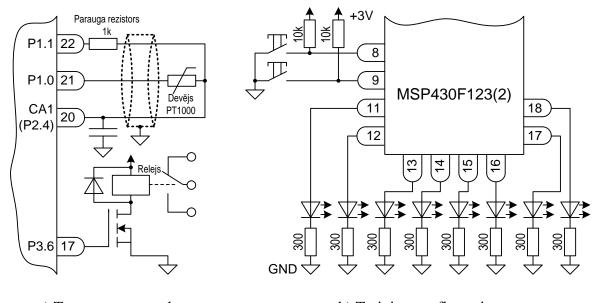

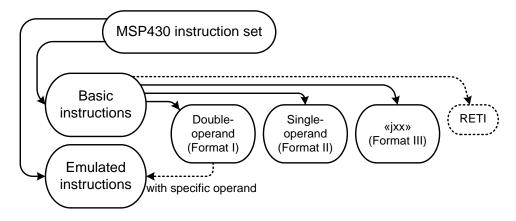

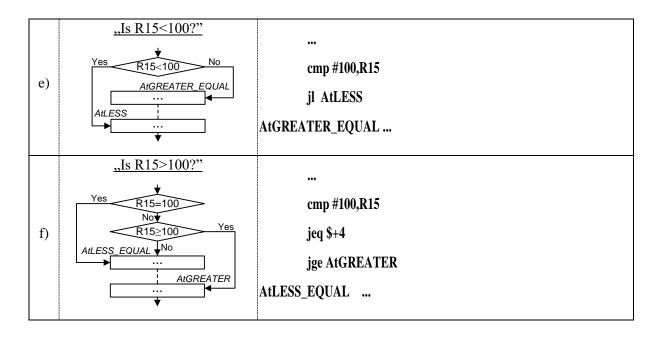

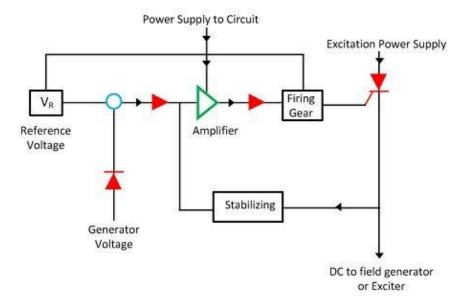

Presently many WSNs are deployed on land, underground and underwater. They face different challenges and constraints depending on their environment. We present five types of WSNs (Yick J, Mukherjee B, Ghosal D., 2008).